NEWS

人工知能の未来、革新的なAIコンピューティングのための「Neuromorphic Chip」! KAISTのY.G.CHOI教授の共同研究チーム、高集積ニューロモルフィック半導体を開発

2021-08-06 hit . 60608

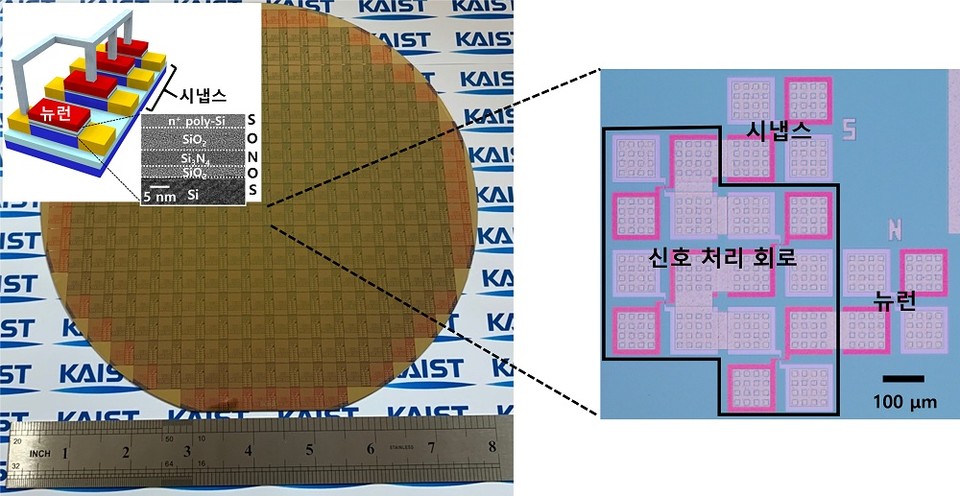

商用化されたCOMS工程で製革された単一トランジスタ基盤ニューロンとシナプス。これを同一ウエハー(8インチ)上に同時集積したニューロモルフィック半導体の3次元及び実写イメージ

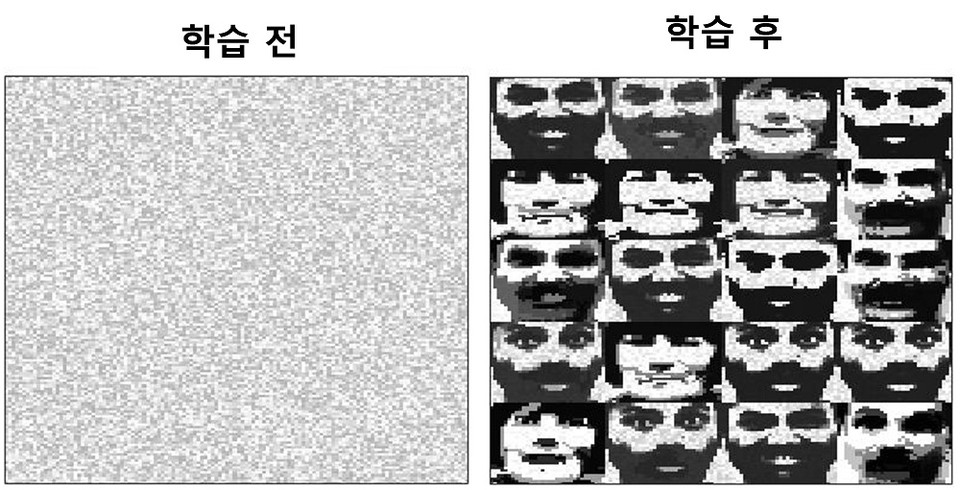

ニューロモルフィック半導体を基盤にした顔面イメージ認識

2021.08.05 13:30

人間の頭脳は数千億個のニューロンが各数万個のシナプスで繋がっている、非常に複雑なネットワーク構造で最大100兆個まで繋がれる。

これを模倣した ニューロモルフィックコンピューティング(Neuromorphic Computing)は

まさにコンピューターアーキテクチャを新しく構想することになる。

進化している実際のデータに対する持続的な学習と適応が必要なロボット工学、自律走行、スマートシティインフラ及び

人工知能(AI)アプリケーションに大きな発展を導かれると見込んでいる。

この中で人工知能コンピューティング向けのニューロモルフィック半導体は既存の半導体が持っている電力問題を解決でき、

データ処理過程の統合もできるため、最もホットな次世代技術として注目を集めている。

人間の脳を模倣して記憶と演算をともに大量で行われるようにすることがニューロモルフィック技術の核心である。

KAIST(カイスト)は電気及び電子工学部のY.G.CHOI(チェ・ヤンギュ)、S.Y.CHOI(チェ・スンユル)教授共同研究チームが

人間の脳を模倣した大規模集積ニューロモルフィック・チップ(半導体)を開発したと発表した。

共同研究チームは単一トランジスターを利用して人間の脳を模倣したニューロンとシナプスで構成されたニューロモルフィック半導体を具現した。

この半導体は商用化されたシリコン標準工程で制作されて、ニューロモルフィックハードウェアシステムの商用化可能性を劇的に高めた。

ニューロモルフィックハードウェアの具現のためには脳と同じく一定の信号が統合される際に

スパイクを発生させるニューロンと、ニューロン間の連結性を覚えるシナプスが必要である。

しかし、デジタルまたはアナログ回路を基に構成されたニューロンとシナプスは広い面積を占めるため、集積度の面で限界がある。

人間の脳が約1,000億個のニューロンと100兆個のシナプスで構成されるとのことから、

実際のモバイル及びモノのインターネット(IoT)装置に使われるためには集積度を改善しなければならない。

これを改善するために様々な素材及び構造基盤のニューロンとシナプスが提案されたが、

その殆どは標準シリコン微細工程技術では製作出来ないため、商用化が難しく、量産適用に問題があった。

研究チームはこの問題を解決するために、すでに幅広く使われている標準シリコン微細工程技術で製作出来る単一トランジスターで

生物学的ニューロンとシナプスの動作を模倣し、これを同一ウエハー(8インチ)上に同時集積してニューロモルフィック半導体を製作した。

製作されたニューロモルフィック半導体は、現在量産されているメモリ及びシステム半導体向けトランジスターと同じ構造で、

トランジスターがメモリ機能や論理演算を行うことは勿論、新しいニューロモルフィック動作が可能ということを実験的に証明したことが意味深い。

従来の量産トランジスターに新しい動作原理を適用して、構造は同じだが機能は全く違うニューロモルフィックトランジスターを製作した。

ニューロモルフィックトランジスターはまるでコインに裏表があるようにニューロン機能もシナプス機能も行う

ヤヌス(Janus)構造の具現が可能ということを世界初に証拠立てた。

研究チームの技術は複雑なデジタル及びアナログ回路基盤で構成されたニューロンを単一トランジスターに切り替えて集積度を大幅高め、

延いては同じ構造のシナプスとともに集積して工程の単純化によるコストダウンもできる新技術である。

既存のニューロン回路構成に要る表面積が21,000単位に比べて、今度開発されたニューロモルフィックトランジスターは6単位以下なので

集積度は約3,500倍以上高い。

研究チームは製作されたニューロモルフィック半導体を基に増幅ゲイン調節、同時性判断などの脳の機能一部模倣し、

文字イメージ及び顔面イメージ認識も可能であることを証明した。

研究チームが開発したニューロモルフィック半導体は集積度の改善とコストダウンなどに役に立ち、

ニューロモルフィックハードウェアの商用化時期の前倒しもできると期待されている。

博士課程のJ.K.HAN(ハン・ジュンギュ)氏は「CMOS(Complementary Metal Oxide Semiconductor)基盤の単一トランジスターを用いて

ニューロンとシナプス動作が可能であることを証明した」とし、「商用化されたCMOS工程を利用してニューロン、シナプス、

そして付加的な信号処理回路を同一ウエハーに同時集積することで、ニューロモルフィック半導体の集積度を改善し、

これによりニューロモルフィックハードウェアの商用化時期をもっと早められる」と述べた。

一方、KAISTのJ.K.HAN博士課程がが第一著者で、同じ学部のJ.Y.OH(オ・ジョンヨプ)博士課程が第二著者として参与した今回の研究は

著名な国際学術誌であるScience Advances(サイエンス・アドバンシス)に

「高度に拡張可能なNeuromorphicハードウェアのための名のスケールCMOSに単一トランジスタニューロン及びシナプス統合

(Co-integration of single transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware)」

とのタイトルで8月4日(現地時間)掲載された。

※本件についてお問い合わせ事項がございましら、当ホームページの「お申込み/お問い合わせ」又は下記の連絡先へご連絡お願い致します。

部署名:SEOIL E&M 企画マーケティンググループ

TEL :+82)2-6204-2033

E-mail : pl@seoilenm.com